티스토리 뷰

입출력 구조 (I/O Structure)

컴퓨터는 여러 형태의 입출력장치를 가진다. 예를들면 키보드, 마우스, 하드디스크, SSD 등이 있고 다양한 장치들을 관리하기 위해 운영체제는 많은 부분들을 입출력장치를 관리하는데 할애하고 시스템에 신뢰성과 성능을 높인다.

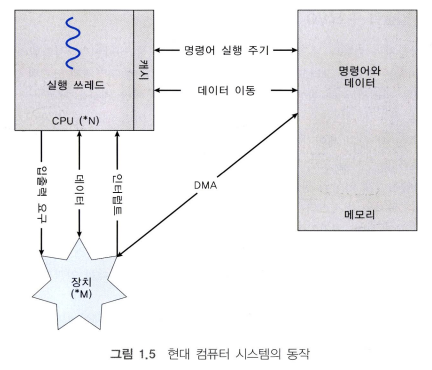

컴퓨터 시스템은 공통 버스에 의해 연결된 여러 개의 장치 제어기와 CPU들로 구성된다. 그리고 각 장치 제어기는 특정 타입의 장치만 담당한다.

장치 제어기는 약간의 로컬 버퍼 저장장치와 특수 목적용 레지스터 집합으로 이루어진다. 이는 장치 제어기가 자신이 제어하는 주변장치와 로컬 버퍼 저장장치 사이의 데이터 전송을 하는데 사용된다.

통상적으로 운영체제는 각 장치 제어기마다 디바이스 드라이버를 가지고 있다. 디바이스 드라이버란, 장치 제어기의 동작을 이해하고 운영체제의 다른 부분들이 해당 장치를 사용할 수 있는 인터페이스를 제공해준다.

디바이스 드라이버는 운영체제가 하드웨어와 연결되는 인터페이스 역할로 하드웨어를 인식하고, 통신하기 위한 소프트웨어이다.

장치 제어기는 하드웨어 디바이스 자체에 내장된 컴포넌트로 하드웨어의 동작을 제어하고 데이터를 처리한다.

입출력 연산

입출력 연산은 장치 내부의 데이터를 외부로 전달하거나 장치 외부의 데이터를 장치 내부에 사용하기 위한 연산이다.

연산을 수행할때, 각 디바이스 드라이버는 장치 제어기의 적절한 레지스터에 필요한 값을 적재한다. 장치 제어기는 이 레지스터 내부 값들을 확인하여 장치에 들어가야하는 값을 로컬 버퍼로 전송하고 연산 완료 신호를 인터럽트로 디바이스 드라이버에 통보한다.

이를 통해 디바이스 드라이버는 제어를 운영체제에 반환하고, 성공적인 결과에는 데이터 혹은 데이터에 대한 포인터를 같이 반환하기도 한다. (동작에 따라 상태 정보를 반환하기도 한다.)

입출력 연산 과정

- 장치 제어기 레지스터에 값 적재

- 장치 제어기는 값을 확인하여 로컬 버퍼로 전송

- 연산

- 연산 완료 후 인터럽트 신호로 디바이스 드라이버에 완료 통보

- 완료된 데이터 정보 반환

- 완료된 상태 정보 반환

입출력 연산

연산 완료 후 발생하는 인터럽트는 대량의 데이터 전송에 높은 오버헤드를 초래한다. 이를 위해 직접 메모리 접근(Direct memory Access, DMA) 장치가 사용된다.

일반적으로는 데이터는 입출력 버퍼에 저장하고 CPU가 이를 읽거나 쓰는 바잇ㄱ으로 시스템 메모리에 직접 읽고 쓸 수 없지만, DMA는 입출력 장치가 CPU 개입 없이 직접 시스템 메모리와 데이터를 교환하도록 한다.

하여 기존 입출력 연산이 바이트 단위로 인터럽트가 발생하지만, DMA는 전체 블록을 모두 전송해야 인터럽트가 발생하여 데이터 전송 과정에서 CPU의 부하를 줄일 수 있다. 하여 DMA를 사용하면 인터럽트가 발생하기 전까지 CPU는 다른 작업을 실행할 수 있다.

이러한 구조는 시스템 버스 대신 스위치 구조를 가진 시스템에서 공유 버스 사이클 경쟁이 없이 다수의 구성요소가 다른 요소들과 동시 통신이 가능하게 만들어 준다.

DMA 입출력 연산 과정

- 입출력 장치가 DMA 컨트롤러에 데이터 전송 요청

- DMA 컨트롤러는 CPU에 인터럽트 발생

- CPU는 DMA 요청 처리

- CPU는 DMA 컨트롤러에게 데이터 전송을 위한 메모리 주소, 전송 방향 등 정보 제공

- DMA 컨트롤러는 데이터 전송 수행

- 전송 완료 시, CPU에 인터럽트 발생

- CPU는 DMA 전송 완료 확인

- 필요에 따라 전송된 데이터 처리

'Computer > Operation System' 카테고리의 다른 글

| [OS] 컴퓨터 시스템 구조 (Computer-System Architecture) (0) | 2024.03.27 |

|---|---|

| [OS] 시스템 콜 (System Calls) (0) | 2024.03.25 |

| [OS] 컴퓨터 시스템의 구성 (1) | 2024.03.15 |

| [OS] 운영체제 서론 (0) | 2024.03.15 |

- Total

- Today

- Yesterday

- New

- 레지스터

- 백준

- 초기화

- 스레드

- 운영체제

- 컴파일

- 함수

- 클래스

- 상속

- 입출력

- 포인터

- malloc

- 수학

- CPU

- 프로세스

- 인터럽트

- 멀티스레드

- const

- 메모리

- 크기

- thread

- dynamic_cast

- 명령어

- 알고리즘

- 구조

- static_cast

- c++

- 할당

- 게임수학

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 | 31 |